SOC-GP-M 平台是一个用于低成本、低功耗SOC项目而开发的SOC设计与验证环境,主要针对以Cortex-M系列为核的SOC项目。

SOC-GP-M 平台由32位处理器内核和一系列可选择、可配置的外设模块组成,这些外设模块针对低成本、低功耗的应用场景进行了设计优化,在兼顾性能的同时大幅度减小了模块的面积。

利用SOC-GP-M平台,用户只需要关注其项目的差异化部分,可以减少模块设计与验证的时间和风险,从而大幅度缩短项目的研发周期,提高项目的成功率。

SOC-GP-M平台包括如下组成部分:

- 32位微处理器内核(需第三方授权)

- 采用Verilog HDL语言设计的各外设模块源代码

- SOC仿真环境与测试程序

- 参考综合脚本

- 基于CMSIS的参考外设驱动

- Cortex-M Keil MDK 项目文件

- FPGA评估板

SOC-GP-A 平台是一个用于高性能SOC项目而开发的设计与验证环境,主要针对以Cortex-A系列为核的高端SOC项目。

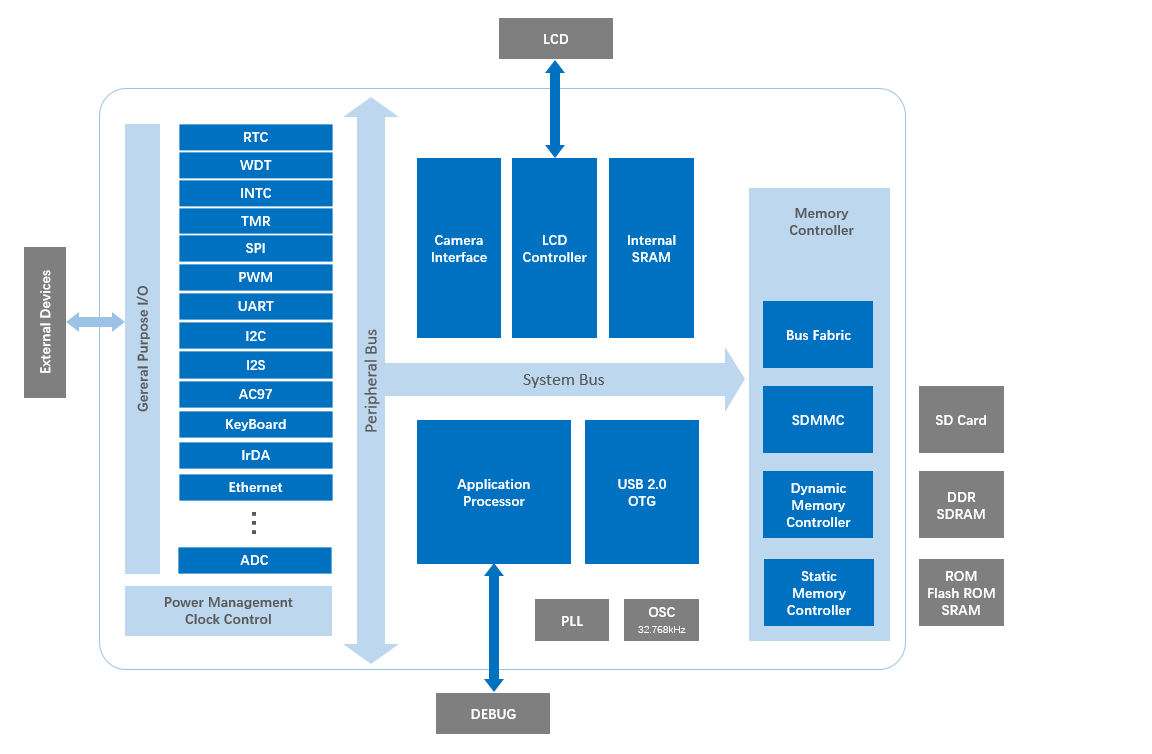

SOC-GP-A 平台由32位处理器内核和一系列可选择的外设模块组成,通过可配置Bus Matrix实现互连(参见下图)。该平台的大多数外设模块可以从本公司直接授权。此外,平台还提供了一套包括多源异步时钟控制、复位控制、功耗控制的系统控制参考设计。

利用SOC-GP-A平台,用户只需要关注其项目的差异化部分,可以减少模块设计与验证的时间和风险,从而大幅度缩短项目的研发周期,提高项目的成功率。

SOC-GP-A平台包括如下组成部分:

- 32位处理器内核(需第三方授权)

- 采用Verilog HDL语言设计的诸多外设模块源代码

- SOC仿真环境与测试程序

- 参考综合脚本

- 参考外设驱动程序

SOC-SP-DVR 平台是一款主要面向音视频应用的架构。

处理器:32位RISC CPU内核,工作频率333MHz,带有音频DSP加速引擎,完成24位精度48K立体声MP3编码、16K单声道编码

视频编码:高性能硬件视频编码器,支持MPEG4、H.264、JPEG等多种格式的视频图像编码,具有WXGA(1024x768)或720p(1280x720)30fps处理能力。支持双码流编码,支持CBR/VBR。采用JPEG编码时,可支持4096x4096的最高分辨率

视频输入接口:一路视频输入端口,支持多种CMOS Sensor,最高分辨率4096x4096,支持ITU BT.601 / BT.656 / BT.1120-SDR / SMPTE 296M标准,同时内置降噪功能和图像缩放功能

音频接口:串行数字音频输入输出,支持PCM、TDM、I2S、AC97等协议

内存接口:16位MDDR/DDR2控制器,支持MDDR/DDR2-400

大容量存储:

- MLC-NAND Flash控制器,24-bit BCH纠错;

- SD/MMC控制器;

- ATA硬盘控制器

USB:USB 2.0 OTG控制器,并集成USB 2.0 OTG PHY

以太网:支持10/100/1000M以太网,采用MII / RMII / RGMII标准接口

无线连接:WIFI MAC接口 或 2.4G RF Transceiver接口,内置RSECC RF编解码纠错引擎

安全引擎:具有多任务处理功能的DES / 3DES / AES / SHA1 / SHA256 / CRC加解密模块